# A Users Guide to the TRB3 and FPGA-TDC Based Platforms

Grzegorz Korcyl, Ludwig Maier, Jan Michel, Andreas Neiser, Marek Palka, Manuel Penschuck, Pawel Strzempek, Michael Traxler, Cahit Ugur

February 22, 2021 - 14:17

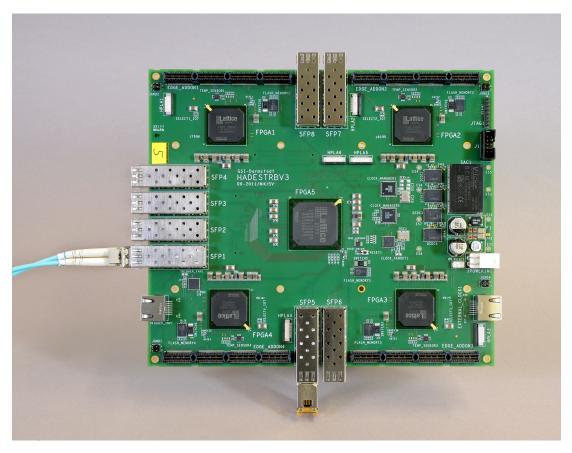

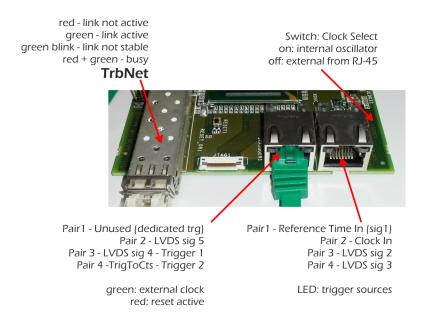

Figure 1: TRBv3 Board.

# **Contents**

| I.   | Resources                                  | 9  |

|------|--------------------------------------------|----|

| 1.   | Code Repository                            | 9  |

|      | 1.1. VHDL                                  | 9  |

|      | 1.2. Software / Documentation              | 9  |

|      | 1.3. Additional Resources                  | 9  |

|      | 1.4. Repository Notes                      | 10 |

|      | 1.4.1. Some Hints for git contributors     | 10 |

|      | 1.5. FPGA designs                          | 10 |

|      | 1.6. Coding Style                          | 11 |

| II.  | General Information                        | 13 |

| 2.   | General Remarks                            | 13 |

|      | 2.1. System Overview for Beginners         | 13 |

|      | 2.2. Beam Time Preparations                | 14 |

|      | 2.3. Hardware Information                  | 14 |

|      | 2.4. Board Identification                  | 14 |

|      | 2.5. Flash Programming                     | 14 |

|      | 2.6. Design Identification                 | 15 |

|      | 2.7. Included Features                     | 16 |

|      | 2.8. Network Addresses                     | 18 |

|      | 2.9. Testing Procedure for New Trb3 Boards | 20 |

|      | 2.10. JTAG                                 | 20 |

|      | 2.11. Data Unpacker                        | 21 |

|      | 2.12. Trigger & Clock Input                | 22 |

|      | 2.13. Power Consumption                    | 22 |

| 3.   | Slow Control Registers                     | 22 |

| III. | . Hardware                                 | 25 |

| 4.   | Measurements                               | 25 |

|      | 4.1. FPGA I/O Performance                  | 25 |

| 5.   | TRB3 Platform                              | 26 |

|      | 5.1 Known Rugs and Limitations             | 26 |

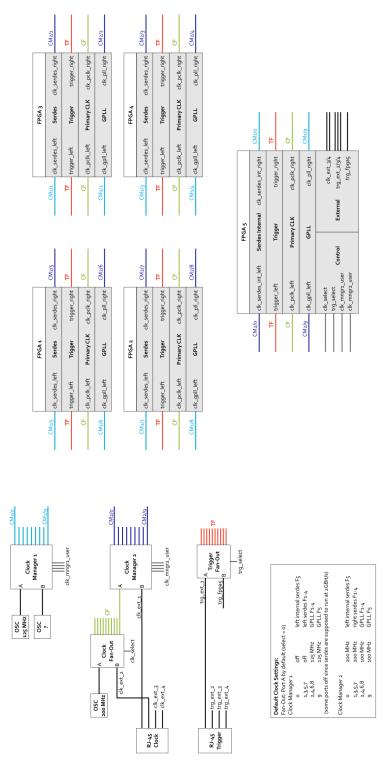

|     | 5.2.  | Clock and Trigger Distribution | 26 |

|-----|-------|--------------------------------|----|

| 6.  | Trb3  | sc                             | 28 |

|     | 6.1.  | Basics                         | 28 |

|     |       | 6.1.1. Powering Schemes        | 28 |

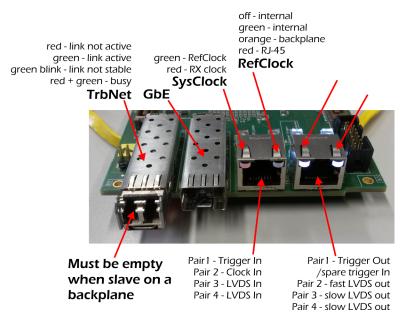

|     |       | 6.1.2. Clock Inputs            | 28 |

|     |       | 6.1.3. Trigger Input/Output    | 29 |

|     |       | 6.1.4. Other I/O               | 29 |

|     |       | 6.1.5. Serial Links            | 30 |

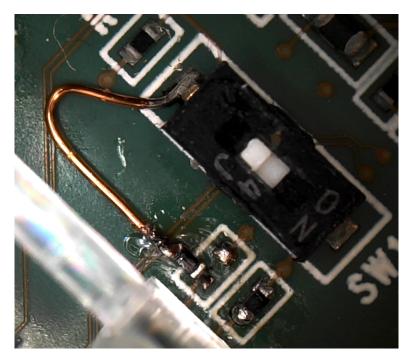

|     |       | 6.1.6. Modifications           | 31 |

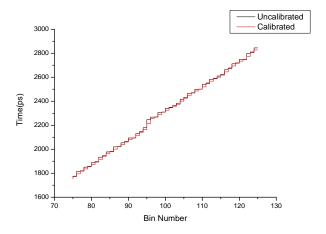

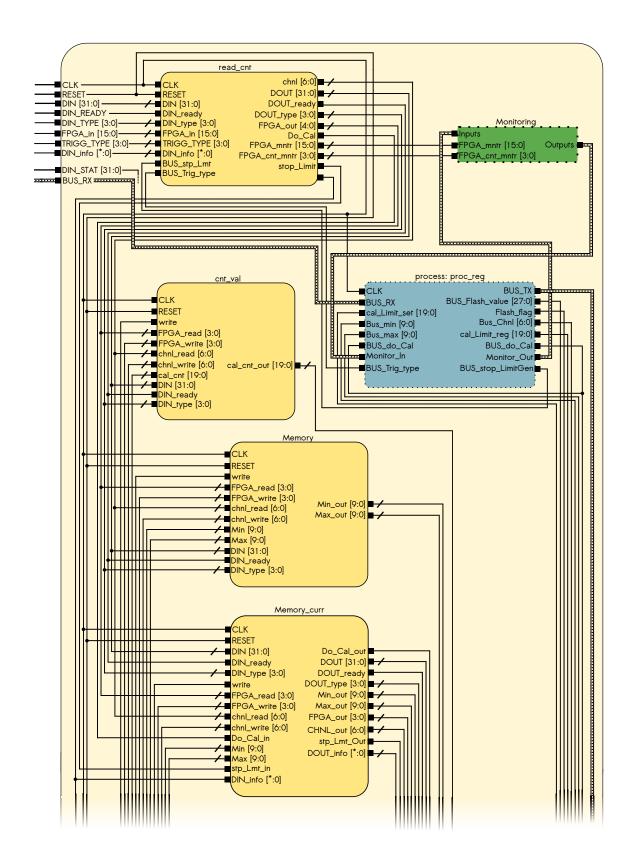

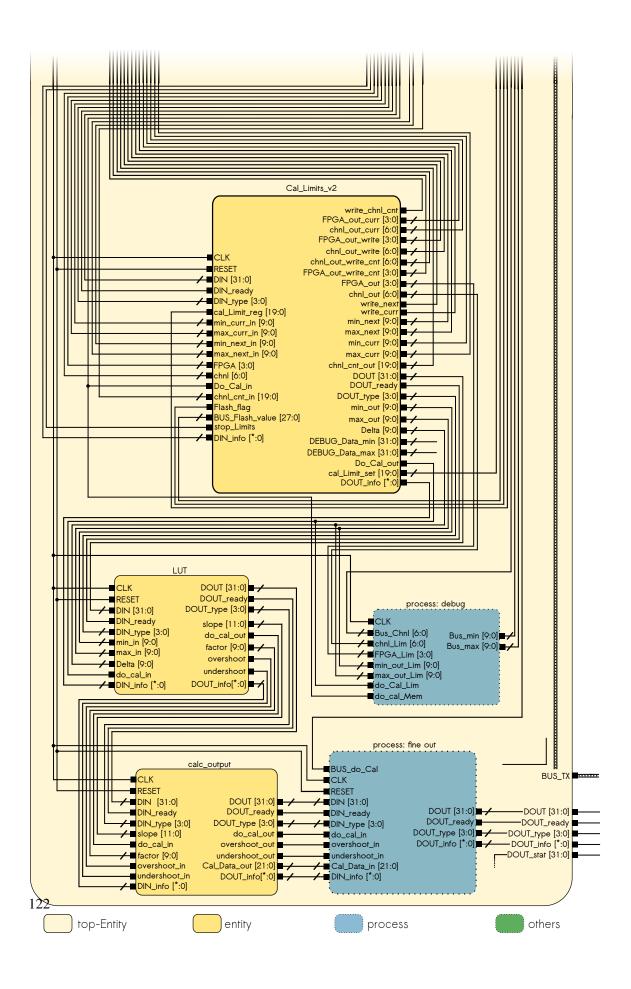

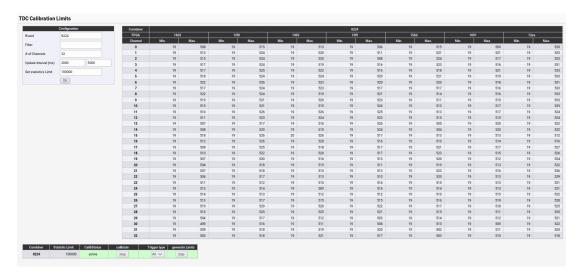

|     | 6.2.  | FPGA based TDC calibration     | 32 |

| 7.  | DiRi  | ch                             | 34 |

| 8.  | Add   | Ons                            | 35 |

|     | 8.1.  | TDC AddOn                      | 35 |

|     | 8.2.  | 32-Pin AddOn                   | 35 |

|     | 8.3.  | Multi-Test-AddOn               | 35 |

|     |       | 8.3.1. Known bugs              | 36 |

|     | 8.4.  | Hub AddOn                      | 36 |

|     | 8.5.  | CTS AddOn                      | 37 |

|     | 8.6.  | General Purpose AddOn          | 37 |

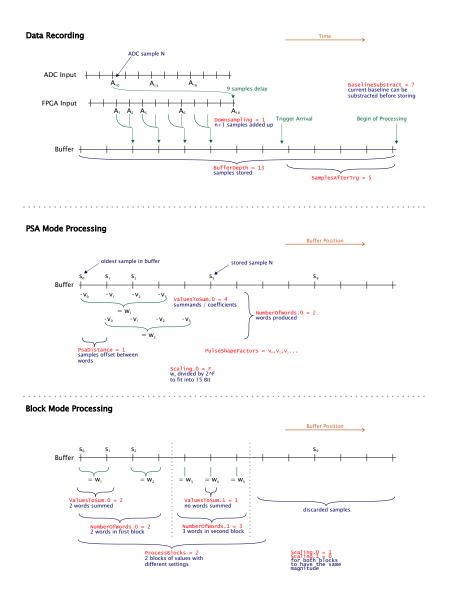

|     | 8.7.  | ADC AddOn                      | 38 |

|     |       | 8.7.1. Data Format             | 38 |

|     |       | 8.7.2. Slow Control Registers  | 40 |

|     | 8.8.  | Padiwa                         | 41 |

| 9.  | Rela  | ted Boards                     | 41 |

|     | 9.1.  | CBM-RICH                       | 41 |

|     | 9.2.  | CBM-TOF                        | 41 |

| IV. | De    | sign Components                | 43 |

|     | DC    | sign components                | 70 |

| 10  | . New | VHDL Project                   | 43 |

| 11. | . TDC |                                | 44 |

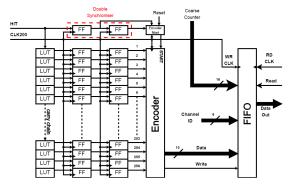

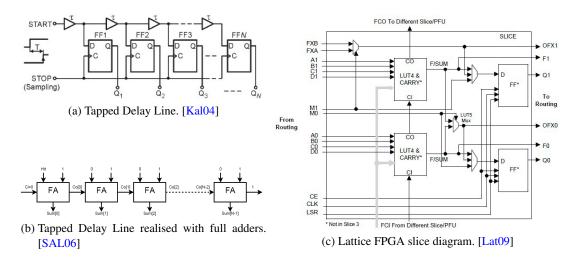

|     | 11.1  | Building Blocks                | 44 |

|     |       | 11.1.1. Fine Time Measurement  | 45 |

|     |       | 11.1.2 Fine Time Calibration   | 45 |

|     | 11.2. | Features                                | 47 |

|-----|-------|-----------------------------------------|----|

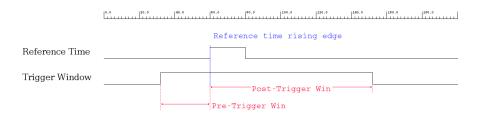

|     |       | 11.2.1. Trigger Window and Trigger Mode | 47 |

|     | 11.3. | Data Format                             | 47 |

|     |       | 11.3.1. TIME DATA                       | 47 |

|     |       | 11.3.2. TDC HEADER                      | 49 |

|     |       | 11.3.3. DEBUG - Status Information      | 49 |

|     |       | 11.3.4. EPOCH Counter                   | 52 |

|     |       | 11.3.5. TDC TRAILER                     | 52 |

|     | 11.4. | Slow Control Registers                  | 53 |

|     | 11.5. | TDC Version Table                       | 57 |

| 12. | Addi  | tional Modules                          | 60 |

|     | 12.1. | SPI Interface                           | 60 |

|     | 12.2. | Forward inputs for trigger              | 62 |

|     | 12.3. | Interfaces                              | 63 |

|     | 12.4. | Flash programming                       | 64 |

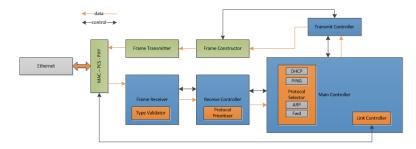

| 13. | GbE   | Data Read-out                           | 67 |

|     | 13.1. | Data Readout                            | 67 |

|     | 13.2. | Addressing                              | 68 |

|     | 13.3. | Configuration                           | 68 |

|     | 13.4. | Monitoring                              | 69 |

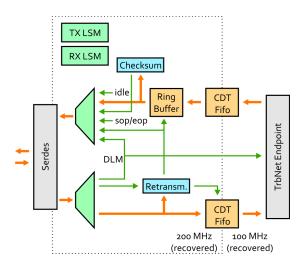

|     | 13.5. | Building Blocks                         | 69 |

|     | 13.6. | Slow Control Registers                  | 69 |

| 14. | GbE   | Slow-Control                            | 70 |

|     | 14.1. | Getting Started                         | 70 |

|     |       | 14.1.1. FPGA design                     | 70 |

|     |       | 14.1.2. Trbnetd                         | 70 |

|     |       | 14.1.3. Trbcmd server                   | 71 |

|     |       | 14.1.4. Usage                           | 72 |

|     |       | 14.1.5. Ping of Death                   | 72 |

|     | 14.2. | Building Blocks                         | 72 |

|     | 14.3. | Slow Control Registers                  | 72 |

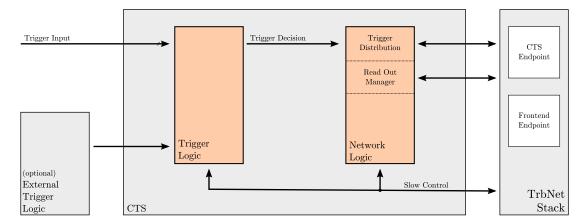

| 15. | CTS   |                                         | 73 |

|     | 15.1. | Features                                | 73 |

|     | 15.2. | Getting Started                         | 73 |

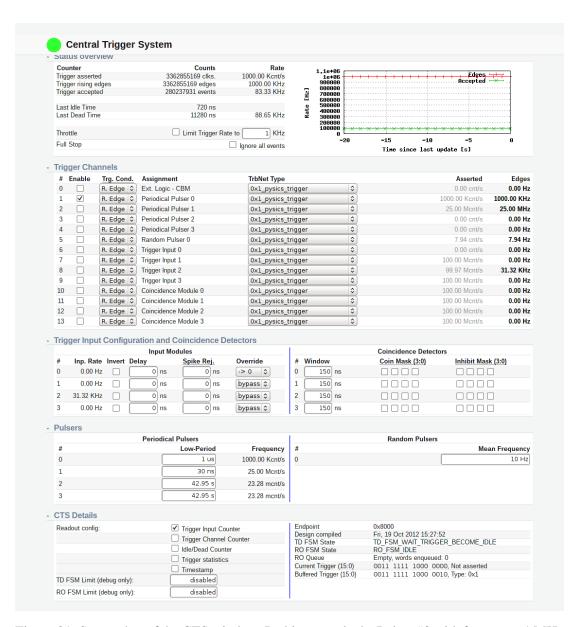

|     |       | 15.2.1. The GUI                         | 73 |

|     | 15.3. | Building Blocks                         | 74 |

|     | 15.4. CTS Network Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

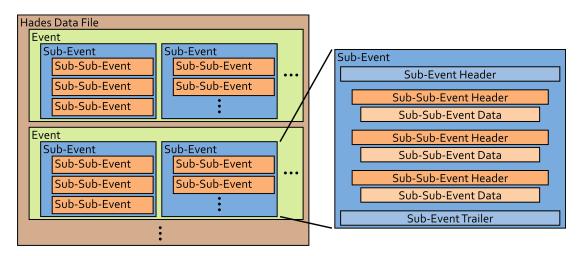

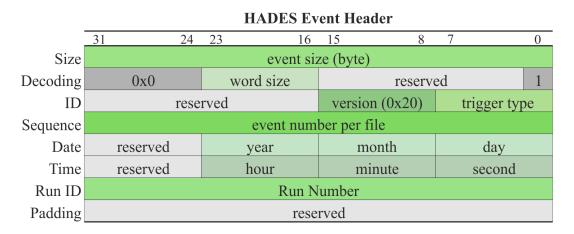

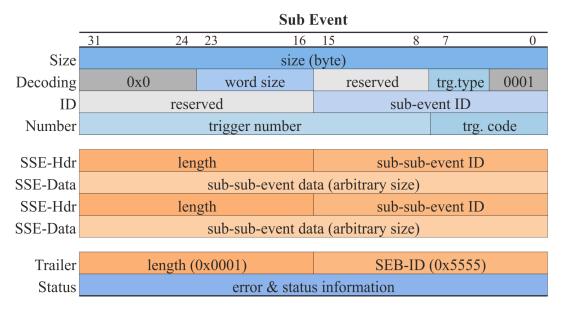

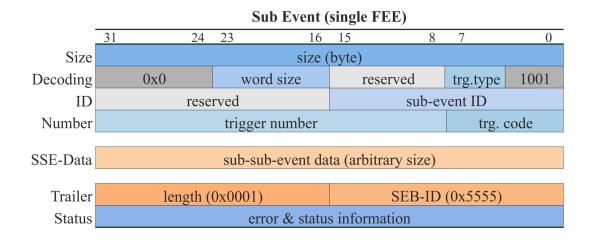

|     | 15.4.1. SubSubEvent Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75         |

|     | 15.4.2. Multiple Event Builders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75         |

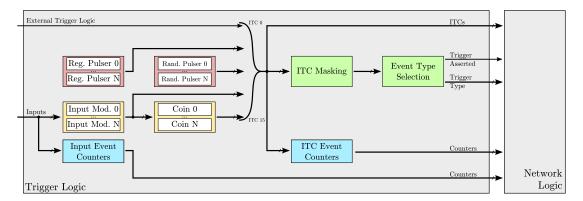

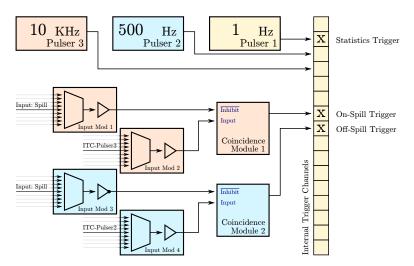

|     | 15.5. Trigger Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77         |

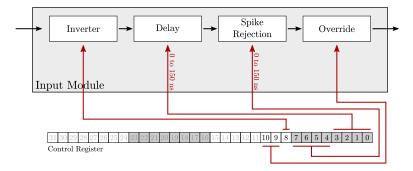

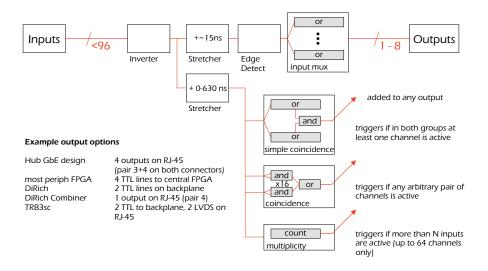

|     | 15.5.1. Input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77         |

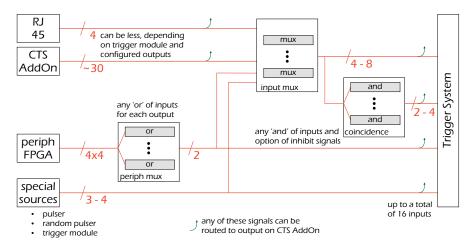

|     | 15.5.2. AddOn Input module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78         |

|     | 15.5.3. Triggers from Peripheral FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 79         |

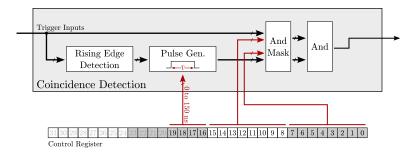

|     | 15.5.4. Coincidence detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79         |

|     | 15.5.5. Pulsers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80         |

|     | 15.5.6. External Trigger Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80         |

|     | 15.5.7. Free-Running with Spill-Dependent Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80         |

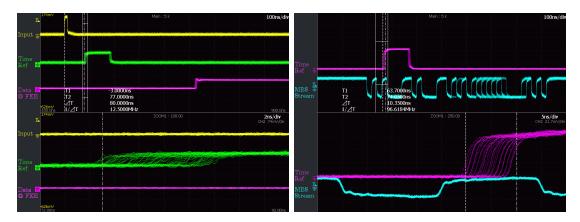

|     | 15.5.8. Latency and Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81         |

|     | 15.6. Slow Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82         |

|     | 15.7. Trigger Generation Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86         |

|     | 15.8. HowTo Implement an External Trigger Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86         |

|     | 15.8.1. The module's interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86         |

|     | 15.8.2. Obtaining a module id and registering the module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89         |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| V.  | Experimental Setups and Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91         |

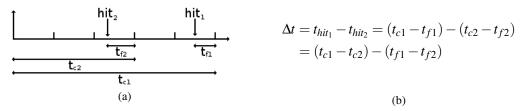

| 16. | . Trigger Time vs Reference Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91         |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| VI. | . Software Quick Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93         |

| 17  | . Distribution Related Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93         |

| •   | 17.1. How to set up SUSE Tumbleweed (64bit) on a PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 93         |

|     | 17.2. How to prepare a Debian distribution (and others)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 96         |

|     | 17.2. The state of property of the property of | ,          |

| 18. | . Software installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97         |

|     | 18.1. User scripts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 98         |

| 19. | . Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99         |

|     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 99         |

|     | 19.2. Preparing DNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|     | 19.3. dnsmasq as an alternative to ISC dhcpd and DNS over /etc/hosts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101        |

|     | 19.3. dnsmasq as an alternative to ISC dhcpd and DNS over /etc/hosts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|     | 19.4. Starting TRBnet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 102        |