# <u>β-NMR/β-NQR VME FREQ SYNTH Module</u>

## General Description

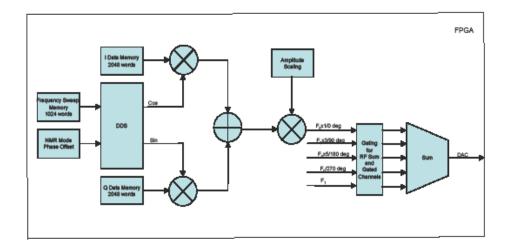

The VME FREQ SYNTH Module (VFS) was designed to generate a complex modulated swept signal summed with a reference frequency. The swept signal may be a single modulated carrier or include the modulated 3<sup>rd</sup> and 5<sup>th</sup> harmonics. Each carrier is independently modulated.

The carriers are synthesized and modulated digitally. The modulation data consists of up to 2048 I,Q pairs sampled at a submultiple of the carrier sample rate. The synthesizer circuit interpolates the I,Q sample rate to match the carrier sample rate before modulation.

## VME Interface SLAVE – A24, D32, D16, D8 (OE)

The VFS resides in 24-bit address space. Selector switches on the printed circuit board configure the base address. The front panel ACC led will indicate a successful VME access to the module.

Supported data transfers:

- D8(EO)

- D16 (aligned only)

- D32

- Read modify write

- D32 block mode

## Address Modifier Selection

The VFS will only respond to A24 address cycles. The AM-SEL led will indicate a valid address modifier.

Supervisory & non-privileged access - 0x39, 0x3A, 0x3B, 0x3D, 0x3E, 0x3F

## **Base Address Selection**

The module selector switches corresponds to address bits A23 – A16 on the VME address bus. Turning a selector switch will set a group of four address bits corresponding to four VME address bits.

#### Table 1 - Base Address Selection

|     | S   | witch | Setting | gs  |     | Address Range   |  |  |  |

|-----|-----|-------|---------|-----|-----|-----------------|--|--|--|

|     | SW2 |       |         | SW1 |     |                 |  |  |  |

| A23 |     | A20   | A19     |     | A16 |                 |  |  |  |

|     | 0   |       |         | 0   |     | 000000 – 00FFFF |  |  |  |

|     | 5   |       |         | 5   |     | 550000 – 55FFFF |  |  |  |

|     | А   |       |         | Α   |     | AA0000 – AAFFFF |  |  |  |

|     | F   |       |         | F   |     | FF0000 – FFFFFF |  |  |  |

## Input Signals

fo CHANNEL1-4 GATE, f1 GATE, FREQ STRB, and fo IDLE IN are NIM input signals. RF Power Trip signal (**RF TRIP IN**) is an analog signal with maximum input level of 5 volts.

## Output Signals

**EXAMPLE 1 CONT** AND A SECOND AND A CONTROL OF THE ADDA OF THE

## **Operating Modes**

#### Single Tone Mode

In this mode the carrier is not modulated. Frequency data is read from the Frequency Sweep Data Memory in the case of the  $f_0 CHANNEL 1 - 4$  and from the VME frequency register in the case of the reference channel  $f_1$ ,  $f_{C0}$  and  $f_{C1}$ . Since the  $f_0 CHANNEL 1 - 4$  data is from the Frequency Sweep Data Memory at least one **FREQ STRB** strobe must be issued. If more than one **FREQ STRB** strobe is issued then operation proceeds according to the Frequency Sweep Data Memory description below.

Quadrature Modulation Mode

In Quadrature Mode I and Q data is read from the I&Q Data Memory. Each channel has its own memory. If an unmodulated carrier is wanted then the I and Q data are set to constant values. There is a separate length register associated with each I&Q Data Memory. When the length is set to zero the last memory location is used as the source of the I and Q data resulting in modulation by a pair of constant values.

Single Frequency

Only the last location (IDLE) in the Frequency Sweep Data Memory is used and at least one **FREQ STRB** strobe must be issued.

## Swept Frequency

One 32-bit word is read from the Frequency Sweep Data Memory for each **FREQ STRB** strobe issued starting at the current location.

## Functional Blocks

#### Frequency Sweep Data Memory

The Frequency Sweep Data Memory has 2048×32-bit frequency values stored in MSB to LSB order as the address increases. The IDLE frequency word must always be initialized. When the sweep reaches the end of the memory as defined by the length register the pointer advances to the IDLE frequency or stops at the Nth frequency according to the setting of the End Sweep Control register. For the special case where the length is set to zero the pointer always points to the IDLE frequency.

## *I&Q Data Memory*

The I&Q memory contains the I and Q modulation values stored in alternating locations in MSB to LSB order as the address increases. Each channel has its own memory with 2048×10-bit I&Q data pairs and its own length register. When the GATE signal for a channel goes to the inactive state, its memory pointer is set to the first location. If the GATE remains active for a period longer than the time it takes to read out the memory, as defined by the length register for that channel, then the pointer advances to the IDLE location or stops at the Nth location according to the setting of the End Sweep Control register. For the special case where the length is set to zero the pointer always points to the IDLE location and the data pair at that location is used.

In order to increase memory depth, a "buffer factor"  $N_C$  has been implemented. The  $N_C$  value sets a delay, based on a 20 MHz I&Q data sample rate, before incrementing the I&Q data memory address.

The I and Q data is in 2's complement format.

## RF TRIP

The  $\Sigma_{OUT}$  **RF** to the RF amplifier is enabled by the **RF TRIP IN** input. An input from the RF detector exceeding the trip level is latched and disables the  $\Sigma_{OUT}$  **RF**. The trip latch must be cleared by writing to the RF Power Status/Trip register in order to enable the output. A trip will occur if no cable is connected to the input. The trip circuit can be effectively disabled by connecting a 50 ohm terminator in place of the external cable.

## GATE Signals

Active levels on the  $f_0$  CHANNEL 1 - 4 and  $f_1$  GATE signals enable the corresponding RF signals and, in Quadrature Modulation mode, enables the modulation. The modulation data pointer is reset whenever the gate is in the inactive state. Readout begins from the first word each time the gate goes active.

## **Limitations**

Maximum frequency sweep strobe rate is 200kHz.

Maximum I&Q data sample rate is 20MHz.

Maximum N<sub>C</sub> buffer factor is 4096.

The minimum RF trip threshold is approximately 115mV and the maximum is approximately 4.85V.

## Table 2 – Memory Map

| Address<br>(HEX) | Reset Value<br>(HEX) | Oper<br>ation | Description                              | Size    |

|------------------|----------------------|---------------|------------------------------------------|---------|

| FFFF<br>C05A     |                      |               | RESERVED                                 |         |

| C05A<br>C058     | XXXX                 | R             | Temperature of FPGA                      | 16 bits |

| C057             | 00                   | R             | RESERVED                                 | 8 bits  |

| C056             | 00                   | R/W           | VME Module Reset                         | 0 bits  |

| C055             | 00                   | R/W           | VME Module Operating Mode                | 1 bit   |

| C054             | 00                   | R/W           | RF Power Trip Status/Reset               | 1 bit   |

| C053             | 80                   | R/W           | RF Power Trip Threshold                  | 8 bits  |

| C052             | 00                   | R/W           | RF Gated Output Select                   | 3 bits  |

| C051             | 00                   | R/W           | RF Pregated Output Select                | 3 bits  |

| C050             | 00                   | R/W           | Anciliary I/O Control                    | 4 bits  |

| C04F             | 00                   | R/W           | Anciliary Output                         | 4 bits  |

| C04E             | 0X                   | R             | Anciliary Input                          | 4 bits  |

| C04C             | 0155                 | R/W           | fo CHANNEL 1 - 4 and f1 Gate Control     | 10 bits |

| C04B             | 3F                   | R/W           | End Sweep Control                        | 6 bits  |

| C04A             | 00                   | R/W           | Frequency Sweep Internal Strobe          | 0 bits  |

| C049             | 00                   | R/W           | Frequency Sweep Address Reset            | 0 bits  |

| C048             | 00                   | R/W           | Frequency Sweep Address Preset           | 0 bits  |

| C046             | 07FF                 | R             | Frequency Sweep Address                  | 11 bits |

| C044             | 0000                 | R/W           | Frequency Sweep Length                   | 11 bits |

| C040             | 00000000             | R/W           | fc1 Frequency Tuning Word                | 32 bits |

| C03C             | 00000000             | R/W           | fco Frequency Tuning Word                | 32 bits |

| C03A             | 0000                 | R             | RESERVED                                 | 16 bits |

| C039             | 00                   | R/W           | fc0,1 Output Select                      | 1 bit   |

| C038             | 80                   | R/W           | fc0,1 Output Scale Factor                | 8 bits  |

| C034             | 0000000              | R/W           | f1 Frequency Tuning Word                 | 32 bits |

| C032             | 0000                 | R             | RESERVED                                 | 16 bits |

| C030             | 07FF                 | R             | f <sub>1</sub> I & Q Data Memory Address | 11 bits |

| C02E             | 0000                 | R/W           | f1 I & Q Data Memory Length              | 11 bits |

| C02C             | 0001                 | R/W           | f1 Nc Buffer Factor                      | 12 bits |

| C02B             | 00                   | R             | RESERVED                                 | 8 bits  |

| C02A             | 80                   | R/W           | f1 Output Scale Factor                   | 8 bits  |

| C028             | 0000                 | R/W           | f1 Phase Modulation                      | 16 bits |

| C026             | 07FF                 | R             | fo CHANNEL 4 I & Q Data Memory Address   | 11 bits |

| C024             | 0000                 | R/W           | fo CHANNEL 4 I & Q Data Memory Length    | 11 bits |

| C022             | 0001                 | R/W           | fo CHANNEL 4 No Buffer Factor            | 12 bits |

| C021             | 00                   | R             | RESERVED                                 | 8 bits  |

| C020             | 80                   | R/W           | fo CHANNEL 4 Output Scale Factor         | 8 bits  |

| C01E             | 0000                 | R/W           | fo CHANNEL 4 Phase Modulation            | 16 bits |

## Table 2 – Con't

| Address<br>(HEX) | Reset Value<br>(HEX) | Oper<br>ation | Description                                      | Size              |

|------------------|----------------------|---------------|--------------------------------------------------|-------------------|

| C01C             | 07FF                 | R             | fo CHANNEL 3 I & Q Data Memory Address           | 11 bits           |

| C01A             | 0000                 | R/W           | fo CHANNEL 3 I & Q Data Memory Length            | 11 bits           |

| C018             | 0001                 | R/W           | fo CHANNEL 3 Nc Buffer Factor                    | 12 bits           |

| C017             | 00                   | R             | RESERVED                                         | 8 bits            |

| C016             | 80                   | R/W           | fo CHANNEL 3 Output Scale Factor                 | 8 bits            |

| C014             | 0000                 | R/W           | fo CHANNEL 3 Phase Modulation                    | 16 bits           |

| C012             | 07FF                 | R             | fo CHANNEL 2 I & Q Data Memory Address           | 11 bits           |

| C010             | 0000                 | R/W           | fo CHANNEL 2 I & Q Data Memory Length            | 11 bits           |

| C00E             | 0001                 | R/W           | fo CHANNEL 2 Nc Buffer Factor                    | 12 bits           |

| C00D             | 00                   | R             | RESERVED                                         | 8 bits            |

| C00C             | 80                   | R/W           | fo CHANNEL 2 Output Scale Factor                 | 8 bits            |

| C00A             | 0000                 | R/W           | fo CHANNEL 2 Phase Modulation                    | 16 bits           |

| C008             | 07FF                 | R             | fo CHANNEL 1 I & Q Data Memory Address           | 11 bits           |

| C006             | 0000                 | R/W           | fo CHANNEL 1 I & Q Data Memory Length            | 11 bits           |

| C004             | 0001                 | R/W           | fo CHANNEL 1 Nc Buffer Factor                    | 12 bits           |

| C003             | 00                   | R             | RESERVED                                         | 8 bits            |

| C002             | 80                   | R/W           | fo CHANNEL 1 Output Scale Factor                 | 8 bits            |

| C000             | 0000                 | R/W           | fo CHANNEL 1 Phase Modulation                    | 16 bits           |

| BFFF<br>A000     | xxxxxxxx             | R/W           | Frequency Sweep Data Memory                      | 2048 x 32<br>bits |

| 9FFF<br>8000     | xxxx                 | R/W           | f1 I & Q Data Memory<br>2's Complement           | 4096 x 10<br>bits |

| 7FFF<br>6000     | xxxx                 | R/W           | fo CHANNEL 4 I & Q Data Memory<br>2's Complement | 4096 x 10<br>bits |

| 5FFF<br>4000     | xxxx                 | R/W           | fo CHANNEL 3 I & Q Data Memory<br>2's Complement | 4096 x 10<br>bits |

| 3FFF<br>2000     | xxxx                 | R/W           | fo CHANNEL 2 I & Q Data Memory<br>2's Complement | 4096 x 10<br>bits |

| 1FFF<br>0000     | xxxx                 | R/W           | fo CHANNEL 1 I & Q Data Memory<br>2's Complement | 4096 x 10<br>bits |

Memory areas between 0000h to BFFFh are uninitialized and not affected by VME resets.

| Address | I&Q Data | Frequency Data |

|---------|----------|----------------|

| N+3     | Q LSB    | Byte 0 (LSB)   |

| N+2     | Q MSB    | Byte 1         |

| N+1     | I LSB    | Byte 2         |

| N+0     | I MSB    | Byte 3 (MSB)   |

## Table 3 - Frequency Sweep and I&Q Data Memory Byte Order

## **Register Description**

## fo CHANNEL 1 Phase Modulation

| ADDR  |    | \$xxxxC000 - C001                     |  |  |  |  |  |  |  |  |  |  |  |  |   |

|-------|----|---------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|---|

| BIT   | 15 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |  | 0 |

| OPER  |    | R/W                                   |  |  |  |  |  |  |  |  |  |  |  |  |   |

| RESET | 0  |                                       |  |  |  |  |  |  |  |  |  |  |  |  |   |

Used to add a phase shift to f<sub>0 CHANNEL 1</sub> RF signal when the module is in NQR mode.

$\Phi_{f_0 \text{ CHANNEL 1}} = (360^\circ \times f_0 \text{ CHANNEL 1} \text{ Phase Modulation value}) \div 65536$

A 0° phase shift is set for  $f_{0 CHANNEL 1}$  RF signal when the module is in NMR mode and this register is ignored.

## fo CHANNEL 1 Output Scale Factor

| ADDR  |                 |     |  | \$xxxx | C002 |  |  |  |  |  |  |  |  |

|-------|-----------------|-----|--|--------|------|--|--|--|--|--|--|--|--|

| BIT   | 7 6 5 4 3 2 1 0 |     |  |        |      |  |  |  |  |  |  |  |  |

| OPER  |                 | R/W |  |        |      |  |  |  |  |  |  |  |  |

| RESET | \$80            |     |  |        |      |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

#### fo CHANNEL 1 Nc Buffer Factor

| ADDR  |    |       |   |  |   |  | \$xx | xxC00 | )4 - C( | 005 |  |  |  |  |  |  |

|-------|----|-------|---|--|---|--|------|-------|---------|-----|--|--|--|--|--|--|

| BIT   | 15 |       |   |  |   |  |      |       |         |     |  |  |  |  |  |  |

| OPER  |    | R R/W |   |  |   |  |      |       |         |     |  |  |  |  |  |  |

| RESET |    | 0     | ) |  | 1 |  |      |       |         |     |  |  |  |  |  |  |

The 12-bit value sets the delay before incrementing the I&Q data memory address.

delay =  $f_0$  CHANNEL 1 NC × 50 nsec

## fo CHANNEL 1 I&Q Data Memory Length

| ADDR  |    |                                                                     |   |  |  |   | \$xx | (xxC0 | 06 - C( | 007 |  |  |  |   |  |  |

|-------|----|---------------------------------------------------------------------|---|--|--|---|------|-------|---------|-----|--|--|--|---|--|--|

| BIT   | 15 | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |   |  |  |   |      |       |         |     |  |  |  | 0 |  |  |

| OPER  |    | R R/W                                                               |   |  |  |   |      |       |         |     |  |  |  |   |  |  |

| RESET |    |                                                                     | 0 |  |  | 0 |      |       |         |     |  |  |  |   |  |  |

The 11-bit value is the number of valid I&Q data pairs stored in the I&Q Data Memory.

#### fo CHANNEL 1 I&Q Data Memory Address

| ADDR  |    |       |   |  |  |       | \$xx | xxC0 | 08 - C | 009 |  |  |  |  |   |  |

|-------|----|-------|---|--|--|-------|------|------|--------|-----|--|--|--|--|---|--|

| BIT   | 15 |       |   |  |  |       |      |      |        |     |  |  |  |  | 0 |  |

| OPER  |    | R R R |   |  |  |       |      |      |        |     |  |  |  |  |   |  |

| RESET |    |       | 0 |  |  | \$7FF |      |      |        |     |  |  |  |  |   |  |

The 11-bit value is the address pointer to the current I&Q data pair in the I&Q Data Memory. The default value points to the IDLE I&Q data pair.

#### fo CHANNEL 2 Phase Modulation

| ADDR  |    | \$xxxxC00A - C00B                     |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-------|----|---------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| BIT   | 15 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |  |  |

| OPER  |    | R/W                                   |  |  |  |  |  |  |  |  |  |  |  |  |  |

| RESET | 0  |                                       |  |  |  |  |  |  |  |  |  |  |  |  |  |

Used to add a phase shift to f<sub>0 CHANNEL 2</sub> RF signal when the module is in NQR mode.

$\Phi_{f_0 \text{ CHANNEL 2}} = (360^\circ \times f_0 \text{ CHANNEL 2} \text{ Phase Modulation value}) \div 65536$

A 90° phase shift is set for f<sub>0 CHANNEL 2</sub> RF signal when the module is in NMR mode and this register is ignored.

#### fo CHANNEL 2 Output Scale Factor

| ADDR  |      | \$xxxxC00C      |  |  |  |  |  |  |  |  |  |  |  |  |

|-------|------|-----------------|--|--|--|--|--|--|--|--|--|--|--|--|

| BIT   | 7    | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |  |

| OPER  |      | R/W             |  |  |  |  |  |  |  |  |  |  |  |  |

| RESET | \$80 |                 |  |  |  |  |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

## fo CHANNEL 2 Nc Buffer Factor

| ADDR  |       |                                                                     |   |   |  |  | \$xx | xxC0 | )E - C( | 00F |  |  |  |  |  |  |

|-------|-------|---------------------------------------------------------------------|---|---|--|--|------|------|---------|-----|--|--|--|--|--|--|

| BIT   | 15    | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |   |   |  |  |      |      |         |     |  |  |  |  |  |  |

| OPER  | R R/W |                                                                     |   |   |  |  |      |      |         |     |  |  |  |  |  |  |

| RESET |       | (                                                                   | ) | 1 |  |  |      |      |         |     |  |  |  |  |  |  |

The 12-bit value sets the delay before incrementing the I&Q data memory address.

delay =  $f_0$  CHANNEL 2 NC × 50 nsec

#### fo CHANNEL 2 I&O Data Memory Length

| ADDR  |    |                                                                              |   |  |  |  | \$xx | xxC0. | 10 - C( | )11 |   |  |  |  |  |

|-------|----|------------------------------------------------------------------------------|---|--|--|--|------|-------|---------|-----|---|--|--|--|--|

| BIT   | 15 |                                                                              |   |  |  |  |      |       |         |     |   |  |  |  |  |

| OPER  |    | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0<br>R R/W |   |  |  |  |      |       |         |     |   |  |  |  |  |

| RESET |    |                                                                              | 0 |  |  |  |      |       |         |     | 0 |  |  |  |  |

The 11-bit value is the number of valid I&Q data pairs stored in the I&Q Data Memory.

## fo CHANNEL 2 I&Q Data Memory Address

| ADDR  |    |                                                                            |   |  |  |  | \$xx | xxC0. | 12 - C( | 013 |       |  |  |  |  |

|-------|----|----------------------------------------------------------------------------|---|--|--|--|------|-------|---------|-----|-------|--|--|--|--|

| BIT   | 15 | <u>15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0</u> |   |  |  |  |      |       |         |     |       |  |  |  |  |

| OPER  |    |                                                                            | R |  |  |  |      |       |         |     | R     |  |  |  |  |

| RESET |    |                                                                            | 0 |  |  |  |      |       |         |     | \$7FF |  |  |  |  |

The 11-bit value is the address pointer to the current I&Q data pair in the I&Q Data Memory. The default value points to the IDLE I&Q data pair.

#### fo CHANNEL 3 Phase Modulation

| ADDR  |    |    |    |    |    |    | \$xx | xxC0 | 14 - C | 015 |   |   |   |   |   |   |

|-------|----|----|----|----|----|----|------|------|--------|-----|---|---|---|---|---|---|

| BIT   | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| OPER  |    |    |    |    |    |    |      | R/   | W      |     |   |   |   |   |   |   |

| RESET |    |    |    |    |    |    |      | (    | )      |     |   |   |   |   |   |   |

Used to add a phase shift to f<sub>0 CHANNEL 3</sub> RF signal when the module is in NQR mode.

$\Phi_{f_0 \text{ CHANNEL 3}} = (360^\circ \times f_0 \text{ CHANNEL 3} \text{ Phase Modulation value}) \div 65536$

A 180° phase shift is set for  $f_{0 CHANNEL 3}$  RF signal when the module is in NMR mode and this register is ignored.

## fo CHANNEL 3 Output Scale Factor

| ADDR  |   |                 |  | \$xxxx | C016 |  |  |  |  |  |  |  |  |

|-------|---|-----------------|--|--------|------|--|--|--|--|--|--|--|--|

| BIT   | 7 | 7 6 5 4 3 2 1 0 |  |        |      |  |  |  |  |  |  |  |  |

| OPER  |   | R/W             |  |        |      |  |  |  |  |  |  |  |  |

| RESET |   |                 |  | \$8    | 30   |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

#### fo CHANNEL 3 Nc Buffer Factor

| ADDR  |    |                                                                              |   |  |  |  | \$xx | (XXC0 | 18 - C( | 019 |  |  |  |  |  |

|-------|----|------------------------------------------------------------------------------|---|--|--|--|------|-------|---------|-----|--|--|--|--|--|

| BIT   | 15 |                                                                              |   |  |  |  |      |       |         |     |  |  |  |  |  |

| OPER  |    | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0<br>R R/W |   |  |  |  |      |       |         |     |  |  |  |  |  |

| RESET |    | (                                                                            | ) |  |  |  |      |       |         | -   |  |  |  |  |  |

The 12-bit value sets the delay before incrementing the I&Q data memory address.

delay =  $f_0$  CHANNEL 3 Nc × 50 nsec

## fo CHANNEL 3 I&Q Data Memory Length

| ADDR  |    |  |   |  |  |  | \$xx | xxC01 | A - C( | )1B |     |  |  |  |  |

|-------|----|--|---|--|--|--|------|-------|--------|-----|-----|--|--|--|--|

| BIT   | 15 |  |   |  |  |  |      |       |        |     |     |  |  |  |  |

| OPER  |    |  | R |  |  |  |      |       |        |     | R/W |  |  |  |  |

| RESET |    |  | 0 |  |  |  |      |       |        |     | 0   |  |  |  |  |

The 11-bit value is the number of valid I&Q data pairs stored in the I&Q Data Memory.

#### fo CHANNEL 3 I&Q Data Memory Address

| ADDR  |    |                                                                                                                                                               |   |  |  |  | \$xx | xxC01 | C - C( | 01D |       |  |  |   |  |

|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|------|-------|--------|-----|-------|--|--|---|--|

| BIT   | 15 | 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0 |   |  |  |  |      |       |        |     |       |  |  | 0 |  |

| OPER  |    |                                                                                                                                                               | R |  |  |  |      |       |        |     | R     |  |  |   |  |

| RESET |    |                                                                                                                                                               | 0 |  |  |  |      |       |        |     | \$7FF |  |  |   |  |

The 11-bit value is the address pointer to the current I&Q data pair in the I&Q Data Memory. The default value points to the IDLE I&Q data pair.

#### fo CHANNEL 4 Phase Modulation

| ADDR  |    |    |    |    |    |    | \$xx | xxC0 | IE - C | 01F |   |   |   |   |   |   |

|-------|----|----|----|----|----|----|------|------|--------|-----|---|---|---|---|---|---|

| BIT   | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| OPER  |    |    |    |    |    |    |      | R/   | Ŵ      |     |   |   |   |   |   |   |

| RESET |    |    |    |    |    |    |      | (    | )      |     |   |   |   |   |   |   |

Used to add a phase shift to f<sub>0 CHANNEL 4</sub> RF signal when the module is in NQR mode.

$\Phi_{f_0 \text{ CHANNEL 4}} = (360^\circ \times f_0 \text{ CHANNEL 4} \text{ Phase Modulation value}) \div 65536$

A 270° phase shift is set for  $f_{0 CHANNEL 4}$  RF signal when the module is in NMR mode and this register is ignored.

#### <u>fo CHANNEL 4 Output Scale Factor</u>

| ADDR  |   |                                                         |  | \$xxxx | C020 |  |  |  |  |  |  |  |  |

|-------|---|---------------------------------------------------------|--|--------|------|--|--|--|--|--|--|--|--|

| BIT   | 7 | 7 6 5 4 3 2 1 0                                         |  |        |      |  |  |  |  |  |  |  |  |

| OPER  |   | 7   6   5   4   5   2   1   0     0           0       0 |  |        |      |  |  |  |  |  |  |  |  |

| RESET |   |                                                         |  | \$8    | 30   |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

#### fo CHANNEL 4 Nc Buffer Factor

| ADDR  |    |   |   |  |  |  | \$xx | (XXC0 | 22 - C | 023 |   |  |  |  |  |

|-------|----|---|---|--|--|--|------|-------|--------|-----|---|--|--|--|--|

| BIT   | 15 |   |   |  |  |  |      |       |        |     |   |  |  |  |  |

| OPER  |    | F | 2 |  |  |  |      |       |        | R   | W |  |  |  |  |

| RESET |    | ( | ) |  |  |  |      |       |        |     | 1 |  |  |  |  |

The 12-bit value sets the delay before incrementing the I&Q data memory address.

delay =  $f_{0 \text{ CHANNEL 4}} N_{C} \times 50 \text{ nsec}$

## fo CHANNEL 4 I&Q Data Memory Length

| ADDR  |    |                                                                    |   |  |  |  | \$xx | xxC0 | 24 - C( | 025 |     |  |  |  |  |

|-------|----|--------------------------------------------------------------------|---|--|--|--|------|------|---------|-----|-----|--|--|--|--|

| BIT   | 15 | 5   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |   |  |  |  |      |      |         |     |     |  |  |  |  |

| OPER  |    |                                                                    | R |  |  |  |      |      |         |     | R/W |  |  |  |  |

| RESET |    |                                                                    | 0 |  |  |  |      |      |         |     | 0   |  |  |  |  |

The 11-bit value is the number of valid I&Q data pairs stored in the I&Q Data Memory.

#### fo CHANNEL 4 I&Q Data Memory Address

| ADDR  |    |  |   |  |  |  | \$xx | (XXC0 | 26 - C | 027 |       |  |  |   |  |

|-------|----|--|---|--|--|--|------|-------|--------|-----|-------|--|--|---|--|

| BIT   | 15 |  |   |  |  |  |      |       |        |     |       |  |  | 0 |  |

| OPER  |    |  | R |  |  |  |      |       |        |     | R     |  |  |   |  |

| RESET |    |  | 0 |  |  |  |      |       |        |     | \$7FF |  |  |   |  |

The 11-bit value is the address pointer to the current I&Q data pair in the I&Q Data Memory. The default value points to the IDLE I&Q data pair.

## f1 Phase Modulation

| ADDR  | \$xxxxC028 - C029 |     |  |  |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------|-----|--|--|--|--|--|--|--|--|--|--|--|--|

| BIT   | 15                |     |  |  |  |  |  |  |  |  |  |  |  |  |

| OPER  |                   | R/W |  |  |  |  |  |  |  |  |  |  |  |  |

| RESET | 0                 |     |  |  |  |  |  |  |  |  |  |  |  |  |

Used to add a phase shift to f<sub>1</sub> RF signal.

$\Phi_{f_1} = (360^\circ \times f_1 \text{ Phase Modulation value}) \div 65536$

## f1 Output Scale Factor

| ADDR  |                 |     |  | \$xxxx | C02A |  |  |  |  |  |  |  |  |

|-------|-----------------|-----|--|--------|------|--|--|--|--|--|--|--|--|

| BIT   | 7 6 5 4 3 2 1 0 |     |  |        |      |  |  |  |  |  |  |  |  |

| OPER  |                 | R/W |  |        |      |  |  |  |  |  |  |  |  |

| RESET | \$80            |     |  |        |      |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

## f1 Nc Buffer Factor

| ADDR  |       |                                                                     |  |  |  |  | \$xx | xxC02 | 2C - C( | )2D |  |  |  |  |  |  |

|-------|-------|---------------------------------------------------------------------|--|--|--|--|------|-------|---------|-----|--|--|--|--|--|--|

| BIT   | 15    | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |  |  |  |  |      |       |         |     |  |  |  |  |  |  |

| OPER  | R R/W |                                                                     |  |  |  |  |      |       |         |     |  |  |  |  |  |  |

| RESET | 0 1   |                                                                     |  |  |  |  |      |       |         |     |  |  |  |  |  |  |

The 12-bit value sets the delay before incrementing the I&Q data memory address.

$delay = f_1 N_C \times 50 nsec$

## f1 I&Q Data Memory Length

| ADDR  |    |  |   |  |  |     | \$xx | xxC02 | 2E - C( | )2F |  |  |  |  |  |  |

|-------|----|--|---|--|--|-----|------|-------|---------|-----|--|--|--|--|--|--|

| BIT   | 15 |  |   |  |  |     |      |       |         |     |  |  |  |  |  |  |

| OPER  |    |  | R |  |  | R/W |      |       |         |     |  |  |  |  |  |  |

| RESET |    |  | 0 |  |  | 0   |      |       |         |     |  |  |  |  |  |  |

The 11-bit value is the number of valid I&Q data pairs stored in the I&Q Data Memory.

#### f1 I&Q Data Memory Address

| ADDR  |         |                                                                              |  |  |  |  | \$xx | xxC0 | 30 - C( | 031 |  |  |  |  |  |  |

|-------|---------|------------------------------------------------------------------------------|--|--|--|--|------|------|---------|-----|--|--|--|--|--|--|

| BIT   | 15      | <u>15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0  </u> |  |  |  |  |      |      |         |     |  |  |  |  |  |  |

| OPER  | R R R   |                                                                              |  |  |  |  |      |      |         |     |  |  |  |  |  |  |

| RESET | 0 \$7FF |                                                                              |  |  |  |  |      |      |         |     |  |  |  |  |  |  |

The 11-bit value is the address pointer to the current I&Q data pair in the I&Q Data Memory. The default value points to the IDLE I&Q data pair.

## f1 Frequency Tuning Word

| ADDR  |    | \$xxxxC034 - C037 |   |

|-------|----|-------------------|---|

| BIT   | 31 |                   | 0 |

| OPER  |    | R/W               |   |

| RESET |    | 0                 |   |

fout = (Frequency Tuning Word × 200 ×  $10^6$ ) ÷  $2^{32}$

Frequency is updated once register \$xxxxC037 (ie. Frequency Tuning Word LSB) is written.

## fc0,1 Output Scale Factor

| ADDR  | \$xxxxC038      |     |  |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------|-----|--|--|--|--|--|--|--|--|--|--|--|

| BIT   | 7 6 5 4 3 2 1 0 |     |  |  |  |  |  |  |  |  |  |  |  |

| OPER  |                 | R/W |  |  |  |  |  |  |  |  |  |  |  |

| RESET | \$80            |     |  |  |  |  |  |  |  |  |  |  |  |

8-bit number that serves as a multiplier for the data pathway before data is delivered to the DAC. It has a LSB weight of  $2^{-7}$  (0.0078125). This yields a multiplier range of 0 to 1.9921875.

## fc0,1 Output Select

| ADDR  |   |   |   | \$xxxx | (C039 |   |   |   |  |  |

|-------|---|---|---|--------|-------|---|---|---|--|--|

| BIT   | 7 | 6 | 5 | 4      | 3     | 2 | 1 | 0 |  |  |

| OPER  | R |   |   |        |       |   |   |   |  |  |

| RESET | 0 |   |   |        |       |   |   |   |  |  |

Sets the unmodulated frequency counter output available at the **FREQ COUNTER RF OUT** port.

bit 0: 0:  $f_{C0}$  on view port 1:  $f_{C1}$  on view port.

## fco Frequency Tuning Word

| ADDR  |    | \$xxxxC03C - C03F |   |

|-------|----|-------------------|---|

| BIT   | 31 |                   | 0 |

| OPER  |    | R/W               |   |

| RESET |    | 0                 |   |

fout = (Frequency Tuning Word × 200 ×  $10^6$ ) ÷  $2^{32}$

Frequency is updated once register \$xxxxC03F (ie. Frequency Tuning Word LSB) is written.

## fc1 Frequency Tuning Word

| ADDR  |    | \$xxxxC040 - C043 |   |

|-------|----|-------------------|---|

| BIT   | 31 |                   | 0 |

| OPER  |    | R/W               |   |

| RESET |    | 0                 |   |

$f_{OUT} = (Frequency Tuning Word \times 200 \times 10^6) \div 2^{32}$

Frequency is updated once register \$xxxxC043 (ie. Frequency Tuning Word LSB) is written.

## Frequency Sweep Length

| ADDR  |    |  |   |  |  |     | \$xx | xxC04 | 14 - C( | )45 |  |  |  |  |  |  |

|-------|----|--|---|--|--|-----|------|-------|---------|-----|--|--|--|--|--|--|

| BIT   | 15 |  |   |  |  |     |      |       |         |     |  |  |  |  |  |  |

| OPER  |    |  | R |  |  | R/W |      |       |         |     |  |  |  |  |  |  |

| RESET |    |  | 0 |  |  | 0   |      |       |         |     |  |  |  |  |  |  |

The 11-bit value is the number of valid 32-bit frequency tuning values stored in the Frequency Sweep memory.

## Frequency Sweep Address

| ADDR  |         |                                              |  |  |  |  | \$xx | xxC04 | 16 - C( | )47 |  |  |  |  |   |  |

|-------|---------|----------------------------------------------|--|--|--|--|------|-------|---------|-----|--|--|--|--|---|--|

| BIT   | 15      | <u>15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0</u> |  |  |  |  |      |       |         |     |  |  |  |  | 0 |  |

| OPER  | R R     |                                              |  |  |  |  |      |       |         |     |  |  |  |  |   |  |

| RESET | 0 \$7FF |                                              |  |  |  |  |      |       |         |     |  |  |  |  |   |  |

The 11-bit value is the current address pointer into the Frequency Sweep memory. The default value points to the IDLE frequency.

## Frequency Sweep Address Preset

| ADDR  |   |   |   | \$xxxx | C048 |   |   |   |

|-------|---|---|---|--------|------|---|---|---|

| BIT   | 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 |

| OPER  |   | R |   |        |      |   |   |   |

| RESET |   |   |   | (      | )    |   |   |   |

Write cycle will preset Frequency Sweep Address pointer registers to the first frequency location. On the next FREQ STRB signal, the frequency at the first location will be loaded.

## Frequency Sweep Address Reset

| ADDR  |   |   |   | \$xxxx | C049 |   |   |   |

|-------|---|---|---|--------|------|---|---|---|

| BIT   | 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 |

| OPER  |   |   |   | F      | 7    |   |   |   |

| RESET |   |   |   | (      | )    |   |   |   |

Write cycle will reset Frequency Sweep Address pointer registers to the default value and loads the IDLE frequency.

## Frequency Sweep Internal Strobe

| ADDR  |   |   |   | \$xxxx | C04A |   |   |   |

|-------|---|---|---|--------|------|---|---|---|

| BIT   | 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 |

| OPER  |   | R |   |        |      |   |   |   |

| RESET |   |   |   | (      | )    |   |   |   |

Write cycle will load **f**<sub>0 CHANNEL 1-4</sub> with the frequency pointed to by the Frequency Sweep Address register.

## End Sweep Control

| ADDR  |   |   |      | \$xxxx | C04B |   |   |   |

|-------|---|---|------|--------|------|---|---|---|

| BIT   | 7 | 6 | 5    | 4      | 3    | 2 | 1 | 0 |

| OPER  | Ŕ |   | R/W  |        |      |   |   |   |

| RESET | 0 |   | \$3F |        |      |   |   |   |

- bit 5: Frequency Sweep End Sweep Mode

- bit 4: f1 I&Q End Sweep Mode

- bit 3: fo CHANNEL 4 I&Q End Sweep Mode

- bit 2: fo CHANNEL 3 I&Q End Sweep Mode

- bit 1: fo CHANNEL 2 I&Q End Sweep Mode

- bit 0: fo CHANNEL 1 I&Q End Sweep Mode

- **o**: stop at Nth if strobes or gate exceed length

- 1: jump to IDLE if strobes or gate exceed length.

#### fo CHANNEL 1 – 4 and f1 Gate Control

| ADDR  |    |    |    |    |     |       | \$xx | xxC04 | 4C - C | 04D |   |   |   |   |   |   |

|-------|----|----|----|----|-----|-------|------|-------|--------|-----|---|---|---|---|---|---|

| BIT   | 15 | 14 | 13 | 12 | 11  | 10    | 9    | 8     | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| OPER  |    | R  |    |    | R/W |       |      |       |        |     |   |   |   |   |   |   |

| RESET |    | 0  |    |    |     | \$155 |      |       |        |     |   |   |   |   |   |   |

- bit 9 8: f1 Gate Control

- bit 7 6: fo CHANNEL 4 Gate Control

- bit 5 4: fo CHANNEL 3 Gate Control

- bit 3 2: fo CHANNEL 2 Gate Control

- bit 1 0: fo CHANNEL 1 Gate Control

**00b**: front panel gate input disabled

- 01b: normal mode (Default)

- 10b: gate pulse inverted

- 11b: front panel gate input ignored and internal gate always ON

#### **Anciliary Input**

| ADDR  | \$xxxxC04E |                 |   |  |   |   |  |   |  |  |

|-------|------------|-----------------|---|--|---|---|--|---|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |   |  |   |   |  | 0 |  |  |

| OPER  |            | Ŕ               |   |  |   | R |  |   |  |  |

| RESET |            | (               | C |  | 0 |   |  |   |  |  |

Reads the **ANCIL I/O 1 - 4** ports, when in input mode (set by register \$xxxxC050).

| bits 7 - 4: | Reserved                  |

|-------------|---------------------------|

| bit 3:      | Anciliary Input Channel 4 |

| bit 2:      | Anciliary Input Channel 3 |

| bit 1:      | Anciliary Input Channel 2 |

| bit 0:      | Anciliary Input Channel 1 |

## Anciliary Output

| ADDR  | \$xxxxC04F |                 |   |  |  |     |   |   |  |  |

|-------|------------|-----------------|---|--|--|-----|---|---|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |   |  |  |     |   | 0 |  |  |

| OPER  |            | Ŕ               |   |  |  | R/W |   |   |  |  |

| RESET |            | (               | C |  |  | (   | ) |   |  |  |

Sets the **ANCIL I/O 1 - 4** ports, when in output mode (set by register \$xxxxC050), to levels set in register.

| bits 7 - 4: | Reserved                   |

|-------------|----------------------------|

| bit 3:      | Anciliary Output Channel 4 |

| bit 2:      | Anciliary Output Channel 3 |

| bit 1:      | Anciliary Output Channel 2 |

| bit 0:      | Anciliary Output Channel 1 |

## Anciliary I/O Control

| ADDR  | \$xxxxC050 |                 |   |  |   |     |  |   |  |  |

|-------|------------|-----------------|---|--|---|-----|--|---|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |   |  |   |     |  | 0 |  |  |

| OPER  |            | Ŕ               |   |  |   | R/W |  |   |  |  |

| RESET |            | (               | C |  | 0 |     |  |   |  |  |

Configures each **ANCIL I/O 1 - 4** ports to NIM inputs or NIM outputs.

| bits 7 - 4: | Reserved                     |

|-------------|------------------------------|

| bit 3:      | Anciliary I/O Channel 4 Mode |

| bit 2:      | Anciliary I/O Channel 3 Mode |

| bit 1:      | Anciliary I/O Channel 2 Mode |

| bit 0:      | Anciliary I/O Channel 1 Mode |

|             |                              |

**0**: NIM input **1**: NIM output

## **RF Pregated Output Select**

| ADDR  |   | \$xxxxC051      |   |  |  |  |   |  |

|-------|---|-----------------|---|--|--|--|---|--|

| BIT   | 7 | 7 6 5 4 3 2 1 0 |   |  |  |  |   |  |

| OPER  |   | R R/W           |   |  |  |  |   |  |

| RESET |   |                 | 0 |  |  |  | 0 |  |

Sets the **RF SEL PREGATED RF OUT** view port to 1 of 6 available pregated RF signals.

000b: f<sub>0</sub> CHANNEL 1 selected (Default) 001b: f<sub>0</sub> CHANNEL 2 selected 010b: f<sub>0</sub> CHANNEL 3 selected 011b: f<sub>0</sub> CHANNEL 4 selected 100b: f<sub>1</sub> selected 101b:  $\Sigma_{OUT}$  selected 110b: invalid; previous setting used 111b: invalid; previous setting used

## **RF Gated Output Select**

| ADDR  |   | \$xxxxC052      |  |  |  |  |  |  |  |

|-------|---|-----------------|--|--|--|--|--|--|--|

| BIT   | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

| OPER  |   | R R/W           |  |  |  |  |  |  |  |

| RESET |   | 0 0             |  |  |  |  |  |  |  |

Sets the **RF SEL GATED RF OUT** view port to 1 of 6 available postgated RF signals.

000b:  $f_{0 \text{ CHANNEL 1}}$  selected (Default) 001b:  $f_{0 \text{ CHANNEL 2}}$  selected 010b:  $f_{0 \text{ CHANNEL 3}}$  selected 011b:  $f_{0 \text{ CHANNEL 4}}$  selected 100b:  $f_{1}$  selected 100b:  $f_{1}$  selected 101b:  $\Sigma_{\text{OUT}}$  selected 110b: invalid; previous setting used 111b: invalid; previous setting used

## **RF Power Trip Threshold**

| ADDR  | \$xxxxC053 |                 |  |     |    |  |  |  |  |  |

|-------|------------|-----------------|--|-----|----|--|--|--|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |  |     |    |  |  |  |  |  |

| OPER  |            |                 |  | R/  | W  |  |  |  |  |  |

| RESET |            |                 |  | \$8 | 30 |  |  |  |  |  |

8-bit value determines the RF Power trip level.

VTRIP = (5 volts × 8-bit value) ÷ 255

## **RF Power Status/Trip Reset**

| ADDR  | \$xxxxC054 |                 |  |  |  |  |  |  |  |

|-------|------------|-----------------|--|--|--|--|--|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

| OPER  |            | R               |  |  |  |  |  |  |  |

| RESET |            | 0               |  |  |  |  |  |  |  |

## bit 0: *RF Power Trip Indicator* 0: normal operation

**1**: Σουτ tripped

Write cycle will clear RF Power Trip latch.

## VME Module Operating Mode

| ADDR  | \$xxxxC055 |                 |  |  |  |  |  |   |  |  |

|-------|------------|-----------------|--|--|--|--|--|---|--|--|

| BIT   | 7          | 7 6 5 4 3 2 1 0 |  |  |  |  |  |   |  |  |

| OPER  |            | R               |  |  |  |  |  |   |  |  |

| RESET | 0          |                 |  |  |  |  |  | 0 |  |  |

bit 0: Operating Mode 0: NMR Mode 1: NQR Mode

Sets the operating mode of the module.

## VME Module Reset

| ADDR  |   |   |   | \$xxxx | C056 |   |   |   |

|-------|---|---|---|--------|------|---|---|---|

| BIT   | 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 |

| OPER  |   |   |   | F      | 7    |   |   |   |

| RESET |   |   |   | (      | )    |   |   |   |

Write cycle will reset all VME registers. Memory locations will be unaffected.

## FPGA Temperature

| ADDR  |    |     |    |    |    |    |   | \$xxx> | C058 |   |   |   |   |   |   |   |

|-------|----|-----|----|----|----|----|---|--------|------|---|---|---|---|---|---|---|

| BIT   | 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8      | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OPER  |    | R R |    |    |    |    |   |        |      |   |   |   |   |   |   |   |

| RESET |    |     |    |    |    |    |   |        | XX   |   |   |   |   |   |   |   |

This register contains the temperature of the FPGA (Stratix II IC). Temperature readings are taken every 500ms and are accurate to  $\pm 1^{\circ}$ C.

|         | Digital Output<br>(Binary, 2's Complement) |         |  |  |  |  |  |

|---------|--------------------------------------------|---------|--|--|--|--|--|

| (°C)    | D15 – D3                                   | D2 – D0 |  |  |  |  |  |

| 150     | 0,1001,0110,0000                           | 000     |  |  |  |  |  |

| 125     | 0,0111,1101,0000                           | 000     |  |  |  |  |  |

| 25      | 0,0001,1001,0000                           | 000     |  |  |  |  |  |

| 0.0625  | 0,0000,0000,0001                           | 000     |  |  |  |  |  |

| 0       | 0,0000,0000,0000                           | 000     |  |  |  |  |  |

| -0.0625 | 1,1111,1111,1111                           | 000     |  |  |  |  |  |

| -25     | 1,1110,0111,0000                           | 000     |  |  |  |  |  |

| -55     | 1,1100,1001,0000                           | 000     |  |  |  |  |  |

## Block Diagram of Module Operation